## MEMS PROCESS SIMULATION AND DEVICE ANALYSIS

**Nora Finch** Sanghamitra Dutta Jonathan Kuhn James Marchetti Tomonori Yamada

**IntelliSense Corporation, USA** NASA, Goddard Space Flight Center, USA Non-member NASA Goddard Space Flight Center, USA **IntelliSense Corporation, USA** Advanced Technologies Co., Ltd.

Non-member Non-member Non-member Non-member

#### Summary

MEMS (Micro-ElectroMechanical Systems) is a key technology for manufacturing in many industrial regions. Today's rapid growth and commercialization of MEMS requires equally rapid product development. Virtual manufacturing, which is usually referred to as computer aided engineering (CAE), enables rapid product development especially in the MEMS world, because computer simulations can address the effects of miniaturization. In this paper, the process of virtual manufacturing on the computer is described step by step through a micro-mirror device, and the numerical results by a CAE tool is compared to the experimental ones obtained from real manufacturing.

Keywords: CAE, MEMS, FEM, BEM, Micro-Mirror

#### 1 Introduction

Miniaturization is becoming increasingly important for commercial manufacturing. Industries such as telecommunications, biomedical, instrumentation, automotive, and aerospace are leading these efforts development (Micro-ElectroMechanical Systems) to scale down devices. Scaling down devices provides opportunities for increased device sensitivity, smaller power requirements, and reduced manufacturing costs.

In order to rapidly and efficiently utilize MEMS technology, engineers are taking advantage of MEMS design software. Simulation tools for MEMS enable engineers to model concepts which cannot be simulated in traditional software packages. Such concepts include the MEMS fabrication process flow and the coupling of electrostatic and mechanical device behavior. Software allows engineers to simulate devices before generating a process flow or to virtually prototype and simulate devices using their process flow, before entering into fabrication.

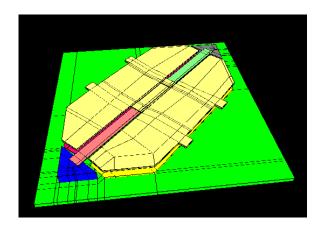

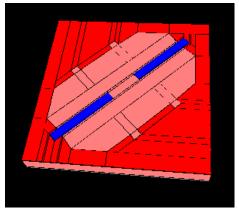

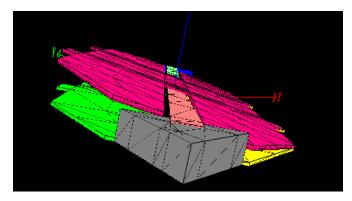

In this paper, the design and analysis of the micro-mirror sub-structure is discussed. This device is currently under development at NASA, Goddard Space Flight Center [1, 2]. Analysis was performed using IntelliSuite™, IntelliSense's CAE tool for MEMS. The structure being analyzed is a two-dimensional tilting aluminum micro-mirror, part of an array of such devices, being developed for Earth and Space science applications such as in the Next Generation Space Telescope. Designed for deep Space applications, the mirror operates at 30K. The mirror itself sits on the sub-structure shown in Figure 1.

Figure 1 Micro-mirror substructure

### 2 Process Simulation

Unlike traditional macro-world mechanical devices and components, the design and functionality of a MEMS device is directly and significantly impacted by the way in which the device is fabricated, i.e. the process sequence and fabrication machine settings which are used. Thus, for MEMS design, it is essential to consider the effect of fabrication on the device analysis results. Process simulation factors which need to be addressed include thin-film material properties, the fabrication sequence, and the mask layouts.

### 2.1 Process Database

Process databases include standard process steps which may exist at any fabrication facility, such as material deposition, wet and dry etching, wafer bonding, and mask definition steps. IntelliSuite™ uses a sequence of these steps, along with the mask geometries, to generate a three-dimensional structure for analysis. These databases can also be customized to include unique or proprietary processes performed for a particular company or at a particular fabrication facility.

Each process step in IntelliSuite<sup>TM</sup> typically includes the machine parameters and any required data, including material properties and mask layouts. The accuracy of the structure generated from these process steps is related to the accuracy of the available process data. Conformal effects and process-induced effects are captured in the development of a three-dimensional structure.

With IntelliSuite<sup>TM</sup>, users create their own process flows from the process database or use one of the included standard foundry templates. Figure 2 shows the start of a process sequence which creates this mirror structure within IntelliSuite. The figure shows:

- 1. Definition of the silicon wafer

- 2. Cleaning of the silicon wafer

- 3. Nitride deposition on top side

- 4. Nickel plating on bottom side

- 5. Definition of mask on top side

- 6. Etching of Si<sub>3</sub>N<sub>4</sub> according to the defined mask on top side

- 7. Etching of Si according to the defined mask on top side

- 8. PolySi deposition on top side

- 9. Etching of PolySi on top side

- 10. Al plating on top side

- 11. Definition of mask on top side

- 12. Etching of Al according to the defined mask on top side

- 13. Au plating on top side

- 14. Definition of mask on top side

- 15. Etching of Au according to the defined mask on top side

- 16. Definition of mask on bottom side

- 17. Etching of Ni according to the defined mask on bottom side

- 18. Etching of Si as sacrifice

- 19. Etching of Si<sub>3</sub>N<sub>4</sub> as sacrifice

Finally the micro-mirror device as shown in Figure 1 is obtained after these 19 processes.

Each process step in IntelliSuite™ provides access to the machine parameters and any required data, including material properties and mask layouts. The accuracy of the analysis of the structure generated from these process steps is related to the accuracy of the available process data. Conformal effects and process-induced effects are captured in the development of the three-dimensional structure.

Definition Si Czochralski 100 Etch Si Clean Pirahna Deposition Si3N4 PECVD Ar Deposition Ni Electroplate Ni\_plating Definition UV Contact Suss Etch Si3N4 Wet Sacrifice Etch Si KOH standard Deposition PolySi LPCVD Standard Etch PolySi General General Deposition Al Sputter Ar-Ambient Definition UV Contact Suss Etch Al Wet PAN Deposition Au E-Beam E-Beam Definition UV Contact Suss Etch Au Standard Standard Definition UV Contact Suss Etch Ni Standard Standard Etch Si KOH standard Etch Si3N4 Wet Sacrifice

Figure 2 Mirror process sequence

#### 2.2 Thin Film Material Database

Thin-film material databases give engineers ready access to material properties. Thin-film material properties are often difficult to characterize and differ from bulk material properties because they vary significantly as a function of fabrication machine settings. It is therefore important to incorporate the correct values in a MEMS design since the use of bulk or otherwise incorrect material property data can produce results which are erroneous and have little relevance to actual results, no matter how accurate the numerical simulation model.

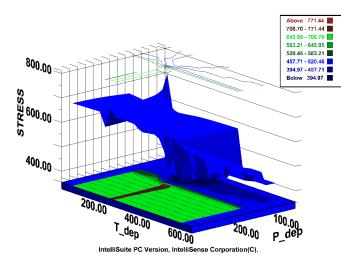

Figure 3 shows a graph produced by the MEMaterial® module of IntelliSuite $^{\text{TM}}$  showing stress as a function of temperature and pressure of deposition for  $\text{Si}_3\text{N}_4$  deposited via PECVD with Argon as the carrier gas (step three of the mirror process). This graph shows large regions of constant stress. However, outside of these areas, the stress varies substantially.

The thin-film material property database consists of experimental results in reliable documents all over the world such as [3-6]. And the required material property is calculated by using the interpolation or extrapolation of these experimental data.

Figure 3 MEMaterial® graph showing stress as a function of the temperature and pressure of deposition

## 2.3 Mask Layout

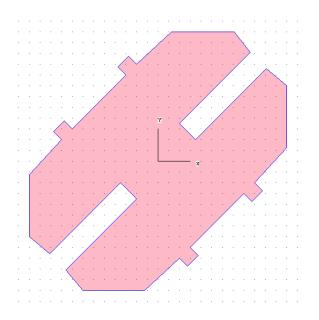

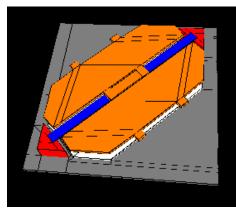

Within the process sequence are a number of mask definition steps. For each, an engineer will create a two-dimensional mask layout. These mask layouts are compatible with DXF and GDSII file formats, standard vendor mask formats. These masks, in conjunction with fabrication deposition and etching processes, will define the three-dimensional geometry of the structure. Figure 4 shows one of the mask layouts for the mirror structure.

Figure 4 Mask layout for the mirror structure

## 3 Virtual Prototyping

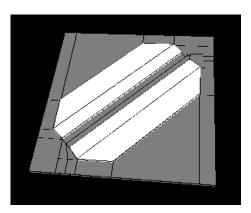

Once a process is generated from a process database or via the use of a standard design template, virtual prototyping is of great benefit. This capability enables engineers to visualize the device at each step of the fabrication process. Here they can modify the process and/or geometry and see the effect of the modification without having to perform multiple fabrication runs. Process tolerances and mask compatibility can also be studied in detail.

### Figure 5 Process steps for the mirror structure

(steps 5, 12, and the final structure)

# 4 Design Communication

The ability to rapidly exchange design files among different collaborative research groups is essential for efficient device design. The process table can also be used as an instrument of communication between such design teams. A single file, consisting of process steps and mask layouts, can be transferred between groups for the development of specific aspects or consultation on designs.

# 5 Device Analysis

Once the masks and fabrication sequence are defined, IntelliSuite<sup>TM</sup> generates a three-dimensional structure for analysis. This step consists of the automatic generation of a coarse finite element mesh, composed of non-linear quadrilateral elements. This finite element mesh also defines the default electrostatic mesh for coupled analysis. Because the contact problem is essential for MEMS device, the electrostatic analysis is carried out by boundary element method (BEM) though the standard structural analysis is carried out by finite element method (FEM) so as not to generated extremely distorted elements on the boundaries, which will contact with each other, in electrostatic analysis.

Inside an IntelliSuite™ analysis module, the finite element and electrostatic meshes are independently refined in areas of interest. Typically, the finite element mesh is refined in areas of high mechanical deformation while the electrostatic mesh is refined in areas of high electrostatic charge. For the micro-mirror, this results in added mechanical elements along the torsional beams and additional electrostatic panels on the underside of the top entity of the substructure as well as on the electrodes.

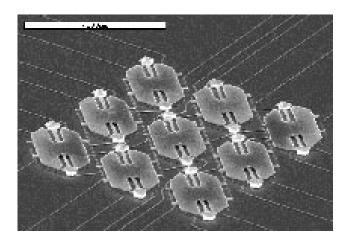

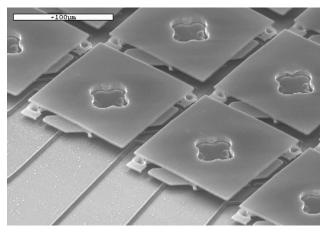

Analysis of the micro-mirror substructure consists of a coupled electro-mechanical analysis. The structure is actuated electrostatically and rotates about the beam connecting the two posts. The mirror surface rotates approximately 10 degrees, until contact is achieved. IntelliSuite's MEMS-specific approach to simulation lifts the restriction of air gap meshing required by non-MEMS tools and can accurately capture the effect of material presstressing in the analysis results. To achieve an optimal design, parametric analyses were performed for a variety of lengths, widths, and thicknesses of the torsional beam. These were compared against fabricated device results.

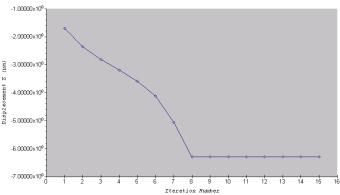

Preliminary analysis results match well with the experimental results (Figure 8). Experimental results show a

snap-down voltage of 14.3 V and release voltage of 7.0 V for this structure. Preliminary simulation results show a snap-down voltage of 17 V. This occurs after eight iterations between IntelliSuite's electrostatic (BEM) and mechanical (FEM) solvers.

Further simulation work will be performed to compare two other beam widths with their corresponding experimental results.

By combining process simulation, virtual prototyping, and a thin-film material database with complete coupled analysis capabilities, IntelliSuite<sup>TM</sup> gives engineers a more complete understanding of their device prior to fabrication.

Figure 6 SEM images showing a 3x3 array of the micro-mirror sub-structures (top) and one of the completed mirror structures (bottom) [2]

Figure 7 Deformed shape

Z Displacement vs Iteration

Figure 8 Iteration study results for the snap-down voltage

### **6 Conclusions**

The simulation approach utilized by IntelliSuite<sup>TM</sup> has been tested in organizations worldwide and proven to be efficient and accurate. Modeling allows for the creation of a geometry and then, based on the analysis results modifications to achieve the desired device performance prior to fabrication. This allows the process to be optimized for production directly, without the usual process transitions and iterations during prototyping.

CAE tools for MEMS can greatly decrease the resources that must be allocated to prototype fabrication and testing by enabling engineers to model the fabrication process in a virtual environment. The impact of CAE tools for MEMS can be seen in the decreased product development time reported by foundries.

- J.L. Kuhn, S.B. Dutta, M.A. Greenhouse and D.B. Mott, "Simulation of Aluminum Micro-mirrors for Space Applications at Cryogenic Temperatures," Third International Conference on Modeling and Simulation of Microsystems, San Diego, CA, USA, March 27-29, 2000.

- S.B Dutta, D.B. Mott, C.A. Allen, J.L. Kuhn, J.W. MacKenty, "Development of 3x3 Array of Individually Addressable Micro-Mirrors for Space Applications, NanoSpace 2000, Houston, TX, USA, January 2000.

- J. A. Aboaf, "Some Properties of Vapor Deposited Silicon Nitride Films Obtained by the Reaction of SiBr4 and NH3," J. Electrochem. Soc., 116 (12), 1969, 1736-1740.

- W. A. P. Claassen, "Ion Bombardment-Induced Mechanical Stress in Plasma-Enhanced Deposited Silicon Nitride and Silicon Oxynitride Films," Plasma Chem. and Plasma Processing, 7 (1),1987,109-124

- A. K. Sinha, H. J. Levinstein, T. E. Smith, G. Quintana, S. E. Haszko, "Reactive Plasma Deposited Si-N Films for MOS-LSI Passivation," J. Electrochem. Soc., 125 (4), Apr. 1978, 601-608.

- Osamu Tabata, Ken Kawahata, Susumu Sugiyama, and Isemi Igarashi, "Mechanical Property Measurements of Thin Films Using Load-Deflection of Composite Rectangular Membranes," Sensors and Actuators, 20, 1989, 135-41.

# References

# **Biographies**

Nora Finch is an Applications Engineer at IntelliSense Corporation. She received a Master of Engineering in High Performance Structures as well as a B.S. in Civil Engineering from MIT. At IntelliSense, she focuses on IntelliSuite<sup>TM</sup> feature development and customer relations.

Tomonori Yamada received his B.S. and M.S. degrees in quantum engineering and systems science from Tokyo University in 1995 and 1997, respectively. Currently he is working in technical support for IntelliSuite™ in the Japanese market.

Dr. Sanghamitra (Mitra) Dutta is a senior member of the engineering staff at NASA Goddard Space Flight Center. Her research interests include semiconductor detectors, accessories, and MEMS component development for Earth and Space science applications. She received her Ph.D. in

Physics from the University of Rochester, NY in 1987.

Dr. Jonathan Kuhn is an engineer in the Mechanical Systems Analysis and Simulation Branch at the NASA Goddard Space Flight Center. He joined NASA in 1997 while completing his dissertation research on micro-mechanics of ceramic matrix composite materials. Since then he has provided analysis and simulation support to

developmental and flight projects including EO-1, DULCE, DCATT, TOPHAT, Constellation X, and NGST-MOS. Dr. Kuhn is now focused on efforts to establish modeling and test methods for the development of MEMS devices.

James Marchetti is a Business Development Manager at IntelliSense Corporation. He is responsible for business development activities for the software unit. He works with customers in the telecommunications and life sciences industries on CAE based device design, MEMS process simulation, and virtual

prototyping. Mr. Marchetti received a B.S. in Chemical Engineering from MIT where his thesis focused on process optimization in manufacturing.